About Us

Our research focuses on high-performance hardware design for next-generation AI and advanced computing systems. We explore novel device, circuit, and architecture solutions to improve memory bandwidth, throughput, and energy efficiency in conventional computing platforms. Our research interests include:

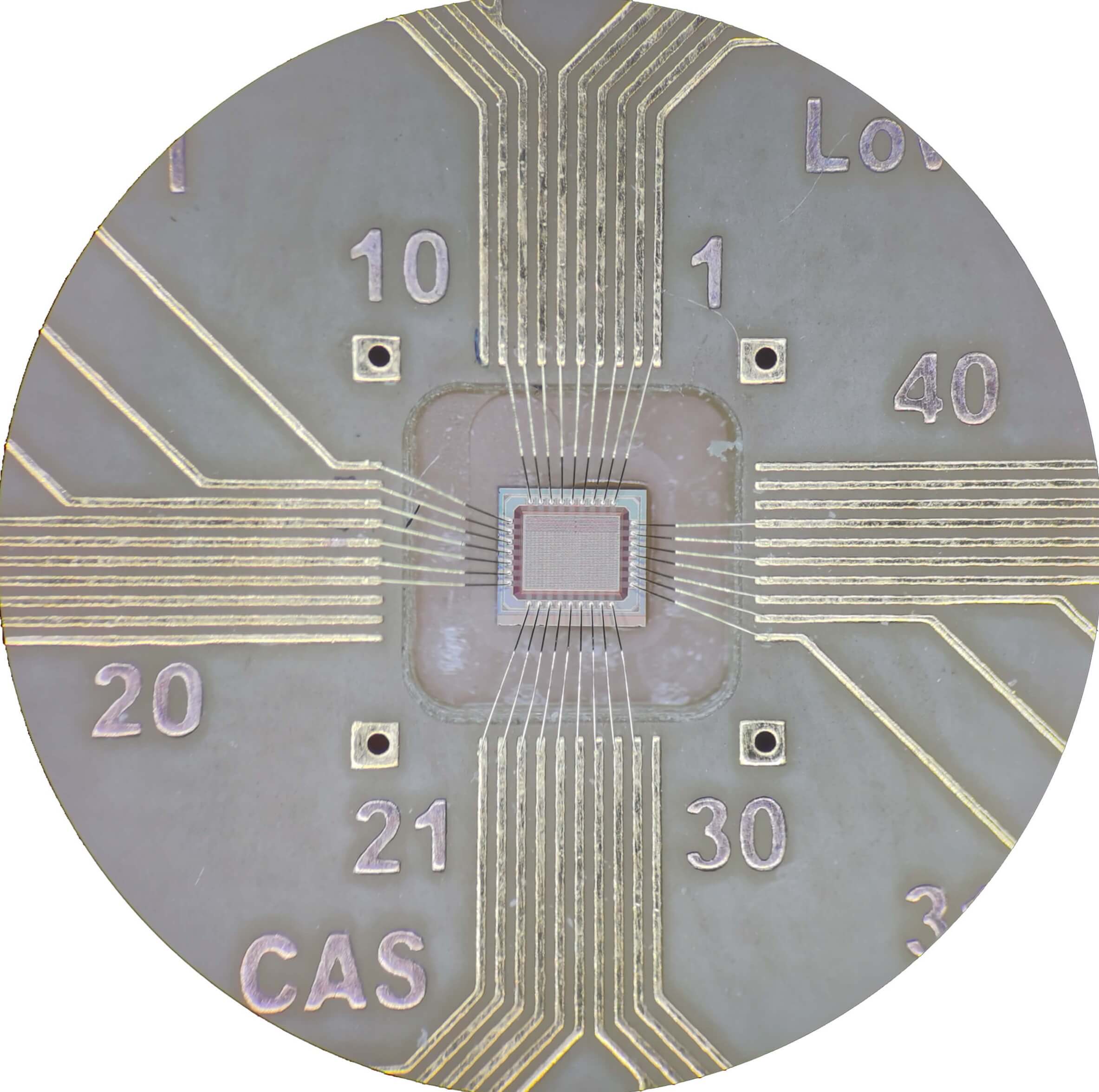

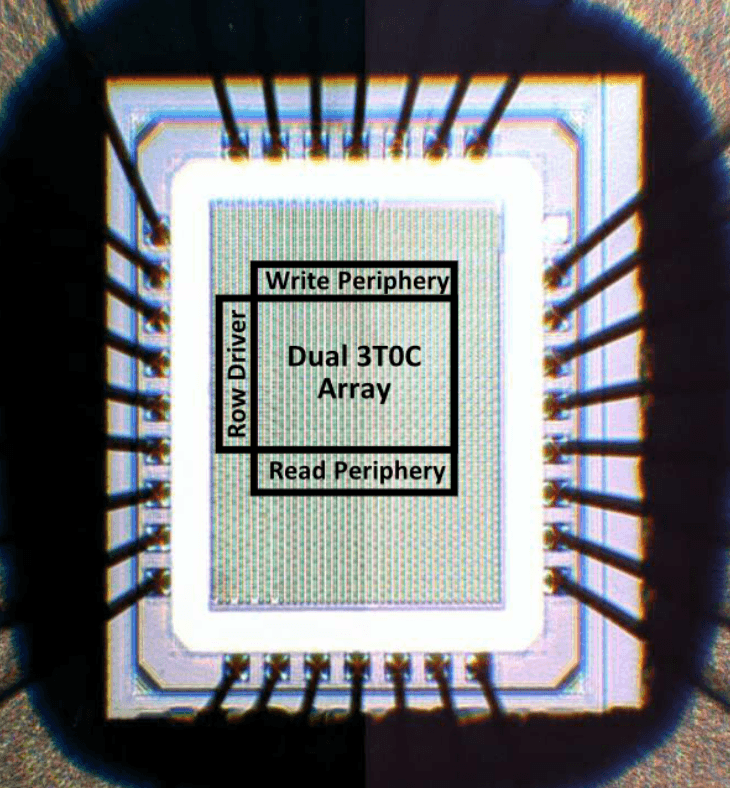

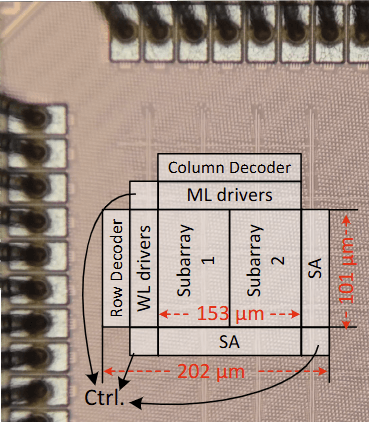

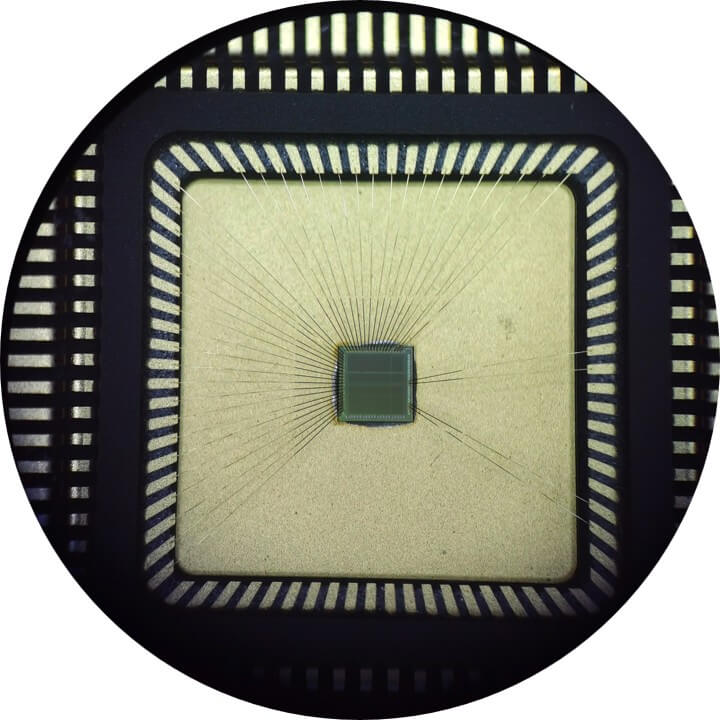

- Domain-Specific Accelerator Design (processing-in-memory accelerators based on SRAM, eDRAM, and emerging memory technologies)

- Cryogenic CMOS Circuit Design (cryogenic memory and computing circuits)

- VLSI System Design (FPGA-based accelerators and System-on-Chip design)